Serial Peripheral Interface (SPI)

The Serial Peripheral Interface (SPI) bus is a synchronous serial communication interface specification used for short distance communication, primarily in embedded systems.

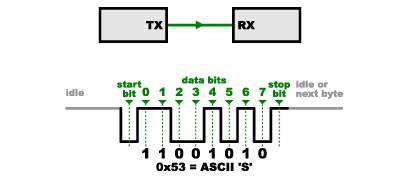

Before going further in to the discussion on the SPI, let's take a look at Asynchronous serial interface and its drawbacks.

- Asynchronous means that data is transferred without support from an external clock signal. This transmission method is perfect for minimizing the required wires and I/O pins, but it does mean we need to put some extra effort into reliably transferring and receiving data.

- A common serial port, the kind with TX and RX lines, is called “asynchronous” (not synchronous) because there is no control over when data is sent or any guarantee that both sides are running at precisely the same rate.

To work around this problem, asynchronous serial connections add extra

start and stop bits to each byte help the receiver sync up to data as it

arrives. Both sides must also agree on the transmission speed (such as

9600 bits per second) in advance. Slight differences in the transmission

rate aren’t a problem because the receiver re-syncs at the start of

each byte.

Asynchronous serial works just fine, but has a lot of overhead in both

the extra start and stop bits sent with every byte, and the complex

hardware required to send and receive data. And as you’ve probably

noticed in your own projects, if both sides aren’t set to the same

speed, the received data will be garbage. This is because the receiver

is sampling the bits at very specific times.

For more detailed discussion on serial communication please see Serial Communication

SPI

SPI is a “synchronous” data bus, which means that it uses separate lines for

data and a “clock” that keeps both sides in perfect sync. The clock is

an oscillating signal that tells the receiver exactly when to sample the

bits on the data line. This could be the rising (low to high) or

falling (high to low) edge of the clock signal; the datasheet will

specify which one to use. When the receiver detects that edge, it will

immediately look at the data line to read the next bit

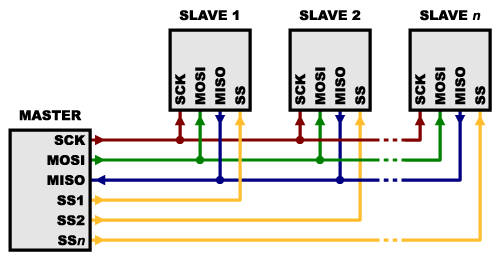

- The SPI bus can operate with a single master device and with one or more slave devices.

- If a single slave device is used, the SS pin may be fixed to logic low if the slave permits it. Some slaves require a falling edge of the chip select signal to initiate an action.

Data transmission

To begin communication, the bus master configures the clock, using a

frequency supported by the slave device, typically up to a few MHz. The

master then selects the slave device with a logic level 0 on the select

line.

During each SPI clock cycle, a full duplex data transmission occurs. The

master sends a bit on the MOSI line and the slave reads it, while the

slave sends a bit on the MISO line and the master reads it. This

sequence is maintained even when only one-directional data transfer is

intended.

- Transmissions normally involve two shift registers of some given word size, such as eight bits, one in the master and one in the slave; they are connected in a virtual ring topology.

- Data is usually shifted out with the most-significant bit first, while shifting a new least-significant bit into the same register. At the same time, Data from the counterpart is shifted into the least-significant bit register.

- After the register bits have been shifted out and in, the master and slave have exchanged register values. If more data needs to be exchanged, the shift registers are reloaded and the process repeats.

- Transmission may continue for any number of clock cycles. When complete, the master stops toggling the clock signal, and typically deselects the slave.

Clock polarity and clock phase

- At CPOL=0 the base value of the clock is zero, i.e. the idle state is 0 and active state is 1.

- For CPHA=0, data are captured on the clock's rising edge (low→high transition) and data is output on a falling edge (high→low clock transition).

- For CPHA=1, data are captured on the clock's falling edge and data is output on a rising edge.

- At CPOL=1 the base value of the clock is one (inversion of CPOL=0), i.e. the idle state is 1 and active state is 0.

- For CPHA=0, data are captured on clock's falling edge and data is output on a rising edge.

- For CPHA=1, data are captured on clock's rising edge and data is output on a falling edge.

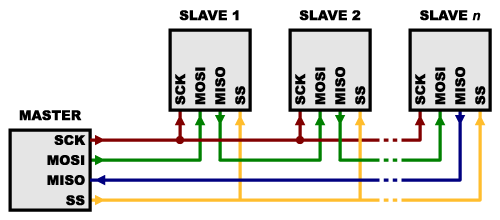

Multiple slaves

There are two ways of connecting multiple slaves to an SPI bus:- In general, each slave will need a separate SS line. To talk to a particular slave, you’ll make that slave’s SS line low and keep the rest of them high (you don’t want two slaves activated at the same time, or they may both try to talk on the same MISO line resulting in garbled data). Lots of slaves will require lots of SS lines;

- On the other hand, some parts prefer to be daisy-chained together, with the MISO (output) of one going to the MOSI (input) of the next. In this case, a single SS line goes to all the slaves. Once all the data is sent, the SS line is raised, which causes all the chips to be activated simultaneously. This is often used for daisy-chained shift registers and addressable LED drivers.

Note that, for this layout, data overflows from one slave to the next, so to send data to any one slave, you’ll need to transmit enough data to reach all of them. Also, keep in mind that the first piece of data you transmit will end up in the last slave.

Advantages of SPI:

- It’s faster than asynchronous serial

- The receive hardware can be a simple shift register

- It supports multiple slaves

Disadvantages of SPI:

- It requires more signal lines (wires) than other communications methods

- The communications must be well-defined in advance (you can’t send random amounts of data whenever you want)

- The master must control all communications (slaves can’t talk directly to each other)

- It usually requires separate SS lines to each slave, which can be problematic if numerous slaves are needed.

Bibliography:

No comments:

Post a Comment